In our second lab day, we worked separately and focused on our own parts. Since we had met the supervisor for the second time, we knew how to do the work from top level. We drew the block diagram, ASM chart and state diagram of vending machine. Apart from this, some group members started researching VHDL code and tried to write the code by themselves.

Here is the work that members have done on our second lab day.

Junlin Guo

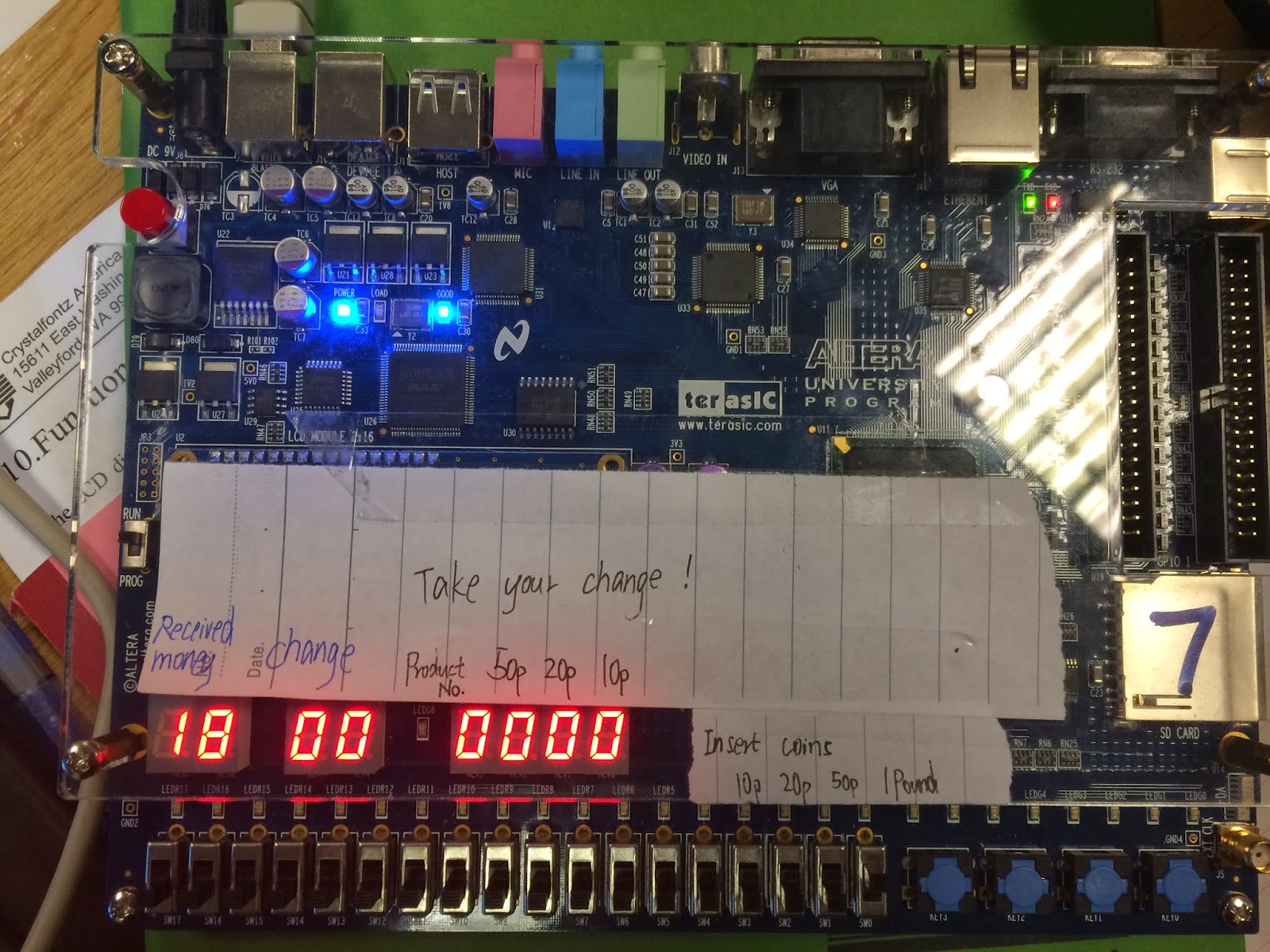

During this week's lab session, I started to write the VHDL code for the coin returner. Firstly, I partially solved the problem that how to determine the number of each type of coin according to the change value. However, there still exists some problems. Since VHDL won't support the loop instruction for an undefined value, I have to find another way to achieve the loop function. I've finished the change function using 50p, and that of 20p is still in progress...

Ye Zhu

Since the state diagram for coin receiver is very complex (21 states, from S0 to S20). I kept on writing the state diagram and starting to draw ASM for coin receiver. I calculated that we needed 5 D-type flip-flops and we should have adder to calculate the sum of input coins D- type flip-flops to represent 5 state bits. However, there was some problems when converting ASM chart to logic circuits.

Xiaotian Zhang

Focus of this week was turned to the ASM chart and related design.

Since my work remains on LCD controller module, four states namely:

- power_up - wait a certain period to ensure voltage has risen to proper level

- initialize - cycle through initialization sequence

- ready - wait for the enable signal and then latch in the instruction

- send - send instruction to lcd

were designed to initialise & function the controller.

The rough code was made yet still need improvement on specific functions of LCD display.

Yuhao Gu

After know the theory of keypad, i started to write the block diagram, i firstly divide it into 3 parts, the keypad, the scanner and the decoder. There will be four scanning signals follow the order 1110-1101-1011-0111-1110. Also the key that pressed will be know by the input signal. Then, the decoder will process the signal from scanner and output a signal that can be received by 7-segment. Actually, for now, i only know how to show the key that have been pressed, but the code to control the products haven't be considered yet.